Phương Trình Đường Tải Tĩnh, Các Phương Pháp Phân Cực Cho Bjt

Việc phân tích hay thiết kế một mạch khuếch đại đòi hỏi sự hiểu biết về đáp ứng dc và ac của hệthống. Người ta thường nhầm lẫn rằng transistor là một linh kiện khuếch đại tín hiệu mà không cầnnguồn năng lượng cung cấp. Thực ra việc khuếch đại tín hiệu ac là từ quá trình chuyển đổi năng lượngtừ nguồn cung cấp dc. Do đó việc phân tích hay thiết kế bất kỳ 1 mạch khuếch đại điện tử đều chứađựng 2 phần: phần dc và phần ac….

Đang xem: Phương trình đường tải tĩnh

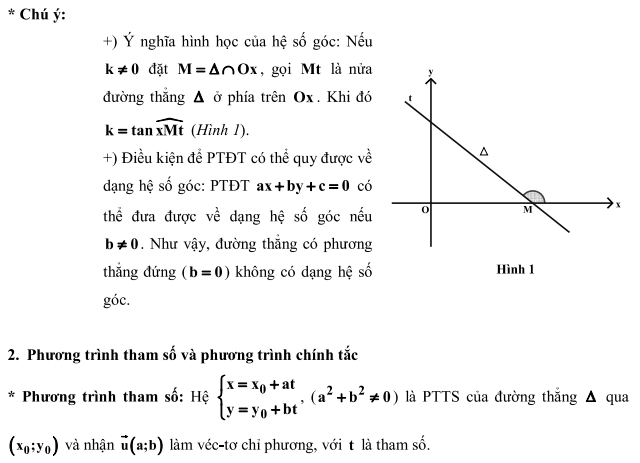

Chương 4: Mạch phân cực transistor. CHƯƠNG 4: MẠCH PHÂN CỰC TRANSISTORI. GIỚI THIỆU: Việc phân tích hay thiết kế một mạch khuếch đại đòi hỏi sự hiểu biết về đáp ứng dc và ac của hệthống. Người ta thường nhầm lẫn rằng transistor là một linh kiện khuếch đại tín hiệu mà không cầnnguồn năng lượng cung cấp. Thực ra việc khuếch đại tín hiệu ac là từ quá trình chuyển đổi năng lượngtừ nguồn cung cấp dc. Do đó việc phân tích hay thiết kế bất kỳ 1 mạch khuếch đại điện tử đều chứađựng 2 phần: phần dc và phần ac. Các mức hoạt động dc của 1 transistor được điều khiển bởi 1 số các thông số bao gồm 1 dãy cácđiểm làm việc có thể có trên các đường đặc tính của transistor. Các dòng điện dc và các mức điện áp dcphải được xác định, một mạch điện phải được xây dựng mà nó sẽ thiết lập điểm làm việc mong muốn –các mạch điện này sẽ được phân tích trong chương này. Hình 4.1: Đặc tuyến ngỏ ra của BJT. Một hệ số phân cực khác rất quan trọng cần chú ý đến: sự lựa chọn và phân cực cho transistor tạiđiểm làm việc mong muốn phải tính đến ảnh hưởng của nhiệt độ. Nhiệt độ làm thay đổi các hệ số nhưβ ac và dòng điện ICEO . Nhiệt độ càng tăng thì dòng điện ICEO tăng làm thay đổi điểm làm việc Q. Do đó cácmạch điện phải thiết kế có sự ổn định nhiệt độ để khi có sự thay đổi nhiệt độ thì sự thay đổi của điểmlàm việc là nhỏ nhất. Sự ổn định của điểm làm việc được chỉ định bởi hệ số ổn định S để xác định mứcđộ thay đổi điểm làm việc phụ thuộc vào sự thay đổi của nhiệt độ. Đối với BJT việc phân cực để hoạt động trong vùng tuyến tính cần phải chú ý: 1. Mối nối B-E phải phân cực thuận với điện áp phân cực vào khoảng 0,6 đến 0,7V. 2. Mối nối B-C phải phân cực ngược với điện áp phân cực nằm trong giới hạn cực đại của transistor.II. Mạch phân cực cho BJT1. Các dạng mạch phân cực:a. Mạch phân cực cố định: Mạch phân cực cố định như hình 4-2 sử dụng transistor npn. 61Chương 4: Mạch phân cực transistor. Hình 4-2. Mạch phân cực cố định. Sơ đồ mạch hình 4-2 có thể chia nguồn cung cấp dc Vcc thành 2 nguồn như hình 4-3. Hình 4.3 Xét mạch vòng BE: Xét mạch vòng phân cực mối nối B-E của hình 4-4. Hình 4.4. Áp dụng định luật Kirchhoff: + VCC − I B R B − V BE = 0 Suy ra dòng điện IB: VCC − V EE IB = RB Xét mạch vòng CE: Mạch vòng phân cực mối nối C-E được vẽ lại như hình 4-5. 62Chương 4: Mạch phân cực transistor. Hình 4.5 Mối liên hệ giữa dòng IB và IC: I C = βI B Aùp dụng định luật Kirchhoff: VCE + I C RC − VCC = 0 Hay VCE = VCC − I C RC Phương trình điện áp VCE: VCE = VC − V E Trong đó VCE là điện áp của 2 điểm C và E còn điện áp V C và VE là điện áp điểm C và E so vớimass. Trong mạch điện trên thì điện áp điểm E bằng không (VE=0V) nên phương trình được viết lại: VCE = VC (4-3) Phương trình điện áp VBE: VCE = VC − V E (4-4) Với VE = 0 nên: V BE = V B (4-5) Hoạt động bảo hòa của transistor: Đối với transistor hoạt động ở vùng bảo hòa thì dòng điện có giá trị cực đại của một mạch đượcthiết kế đặc biệt. Thay đổi thiết kế thì mức bảo hòa tương ứng có thể tăng hoặc giảm và dĩ nhiên giá trịbảo hòa lớn nhất xác định bởi dòng điện Ic cực đại được cung cấp trong bảng thông số của transistor. Các điều kiện bảo hòa thường nên tránh bởi vì mối nối CB không còn phân cực ngược dẫn đến tínhiệu ngỏ ra mạch khuếch đại bị méo dạng. Điểm hoạt động trong vùng bảo hòa trình bày ở hình 4-7a.chú ý rằng trong vùng bảo hòa thì các đường cong đặc tính được nối lại với nhau và điện áp C E nằm tạimức hoặc thấp hơn mức điện áp VCesat. Dòng điện Ic có giá trị tương đối lớn trên đường cong đặc tính. Hình 4.7. Nếu ta dùng các đường cong xấp xỉ như hình 4-7b để xác định nhanh các mức giá trị trong vùng bảohòa. Trong hình 4-7b, dòng điện tương đối cao còn điện áp VCE xem như bằng 0V. Áp dụng định luậtOhm để tính điện trở mối nối CE: 63Chương 4: Mạch phân cực transistor. Áp dụng kết quả trên ta vẽ lại mạch có cấu hình như hình 4-8. Đối với mạch phân cực cố định khi transistor ở chế độ bảo hòa thì sơ đồ mạch như hình 4-9, điệnáp rơi trên R chính bằng Vcc và dòng điện Ic bảo hòa có giá trị: Hình 4-8. Xác định ICsat. Hình 4-9. Xác định ICsat của mạch phân cực. ** Mạch phân cực cố định ổn định cực emitter: Mạch phân cực dc hình 4-10 có thêm 1 điện trở tại cực Emitter để cải thiện mức độ ổn định củacấu hình mạch phân cực cố định. Hình 4-10. Mạch phân cực BJT có thêm điện trở cực E. Hình 4-11. Xét mạch vòng BE: Hình 4-10 có thể vẽ lại như hình 4-11, áp dụng định luật Kirchhoff được phương trình: + VCC − I B R B − V BE − I E R E = 0 (4-7) Phương trình dòng điện ở chương 3: I E = ( β + 1) I B (4-8) Thế vào pt (4-15) được: + VCC − I B R B − V BE − ( β + 1) I B R E = 0 Rút gọn và suy ra dòng điện IB: VCC − V BE IB = (4-9) R B + ( β + 1) R E Chú ý rằng chỉ có 1 sự khác nhau trong phương trình dòng điện IB so với mạch phân cực cố định làthành phần (β+1)RE. Từ phương trình (4-17) ta có mạch điện tương đương như hình 4-12. Nếu nhìn từ phía điện áp V BEthì điện trở RE phản hồi trở lại dòng điện ngỏ vào IB bởi hệ số (β+1). Mặc khác điện trở cực E – là mộtphần của mạch vòng cực CE – có giá trị (β+1)RE đối với mạch vòng BE. Do β thường có giá trị vào 64 Ri = ( β + 1) R E (4-10)Chương 4: Mạch phân cực transistor.khoảng 50 hoặc cao hơn nên điện trở cực E sẽ trở thành một điện trở thật lớn đối với ngỏ vào cực B Enhư hình 4-13. Điện trở ngỏ vào: Hình 4-12. Hình 4-13. Hình 4-14. Xét mạch vòng CE: Mạch vòng phân cực mối nối C-E được vẽ lại như hình 4-14. Áp dụng định luật Kirchoff về áp: + I E R E + VCE + I C RC − VCC = 0 Thay thế IE ≅ IC và suy ra điện áp VCE: VCE = VCC − I C ( RC + R E ) (4-11) Điện áp cực Emitter VE: VE = I E RE (4-12) Điện áp cực Collector VC: VC = VCE + V E (4-13) Hay VC = VCC − I C RC (4-14) Điện áp cực Base VB: V B = VCC − I B R B (4-15) Hay V B = V BE + V E (4-16)b. Mạch phân cực bằng cầu phân áp: Mạch phân cực bằng cầu phân áp dc hình 4-15. Có 2 phương pháp phân tích mạch: phân tích chínhxác và phân tích gần đúng. Hình 4-15. Phân tích chính xác: 65Chương 4: Mạch phân cực transistor. Mạch điện ngỏ vào có thể vẽ lại như hình 4-18. Dùng mạch tương đương Thevenin và cần xácđịnh điện trở tương đương Thevenin và điện áp Thevenin: Xác định điện trở Thevenin RTh: ngắn mạch nguồn điện áp như hình 4-16. RTh = R1 R 2 (4-17) Xác định điện áp Thevenin Eth: mạch điện như hình 4-17. R 2VCC (4-18) E Th = V R 2 = R1 + R 2 Mạch đương tương Thevenin như hình 4-18 và dòng điện I B có thể xác định bằng định luậtKirchhoff: E Th − I B RTh − V BE − I E R E = 0 Thay thế dòng IE = (β + 1) IB vào suy ra dòng IB: E Th − V BE IB = (4-19) RTh + ( β + 1) R E Hình 4-16. Xác định RTh. Hình 4-17. Xác định ETH. Hình 4-18. Mạch tươngđương. Phương trình mạch vòng CE không có gì thay đổi – kết quả được: VCE = VCC − I C ( RC + R E ) (4-20) Phân tích gần đúng: Cấu hình mạch phân áp ngỏ vào có thể thay thế bằng mạch điện hình 4.19. Điện trở Ri là điện trởtương đương giữa cực B và mass – đã xác định ở phần trước bằng ( β + 1) RE . Nếu Ri lớn hơn nhiều sovới R2 thì dòng IB nhỏ hơn dòng qua R2 rất nhiều có nghĩa là dòng I1 xấp xỉ bằng dòng I2. Khi dó điện áptrên R2 bằng điện áp VB xác định bởi phương trình: R 2VCC (4-21) VB = R1 + R 2 Có thể xem Ri = (β + 1) RE ≅ βRE thì điều kiện để thỏa mãn phép tính gần đúng là βR E ≥ 10R 2 Xác định điện áp VE: V E = V B − V BE Xác định dòng điện IE: VE IE = RE Và có thể xem: I CQ ≅ I E Điện áp VCEQ: VCEQ = VCC − I C ( RC + R E ) 66Chương 4: Mạch phân cực transistor. Điểm tĩnh Q không phụ thuộc vào hệ số β. VCE = VCC − I C ( RC + R E ) Hình 4-19.c. Mạch phân cực hồi tiếp từ collectror : Mạch phân cực hồi tiếp điện áp như hình 4-20. Hình 4.20 Hình 4.21. Xét mạch vòng BE: Hình 4-20 có thể vẽ lại như hình 4-21, áp dụng định luật Kirchhoff được phương trình: + VCC − I C RC − I B R B − V BE − I E R E = 0 ” Có thể xem I C ≅ I C = βI B ” I E ≅ IC Thế vào phương trình trên được: + VCC − V BE − βI B ( RC + R E ) − R B I B = 0 Suy ra dòng điện IB: VCC − V BE (4-23) IB = R B + β ( RC + R E ) Tổng quát, phương trình dòng IB có dạng như sau: V” IB = R B + βR ” Do IC = β IB nên: βV ” I CQ = R B + βR ” Do βR’ lớn hơn RB rất nhiều nên có thể xem: βV ” βV ” V ” I CQ = ≅ = R B + βR ” βR ” R” 67Chương 4: Mạch phân cực transistor. Cho thấy ICQ không phụ thuộc vào hệ số β. Xét mạch vòng CE: Hình 4-20 có thể vẽ lại như hình 4-21. Hình 4.21 Áp dụng định luật Kirchhoff được phương trình: I E R E + VCE + I ” C RC − VCC = 0 Do I’C ≅ IC và IE ≅ IC nên: I C ( R E + RC ) + VCE − VCC = 0 hay VCE = VCC − I C ( R E + RC ) (4-24)2. Phân tích đường tải: Xét mạch điện như hình 4.22 Hình 4.22 • Đường tải dc (DCLL – DC load line) Mạch điện hình 4-22 thiết lập một phương trình ngỏ ra diễn tả mối liên hệ giữa 2 biến IC và VCEnhư: VCE = VCC − I C RC Hay: 1 V IC = − VCE + CC (4.25) RC RC Phương trình 4.25 chính là phương trình đường tải dc của mạch hình 4.22. Đồ thị đường tải DCLLcủa mạch hình 4.22 trên đường đặc tuyến ngỏ ra của transistor trên hình 4.23 68Chương 4: Mạch phân cực transistor.

Xem thêm: Review Khóa Học Ielts Online Giúp ‘Đọc Thông Viết Thạo’ Chất Lượng Nhất

Xem thêm: Đồ Án Thiết Kế Nội Thất Chung Cư, Hình Ảnh Workshop Cbs

Hình 4.23: Đường tải DCLL. Nếu dòng điện IB thay đổi bởi các giá trị khác nhau của R B thì điểm tĩnh Q sẽ di chuyển lên hoặc dichuyển xuống như hình 4-24. Nếu điện áp Vcc và IB giữ cố định và điện trở Rc thay đổi thì đường tải sẽdịch chuyển như hình 4-25. Hình 4-24. Hình 4-25 Nếu RC cố định và Vcc thay đổi thì đường tải dịch chuyển như hình 4-26. Hình 4.26 • Đường tải ac (ACLL – AC load line): Ta có phương trình ngõ ra chỉ với tín hiệu ac: ic ( RC R L ) + vce = 0 hay: 1 ic = − vce ( RC R L ) mà iC = ic + I CQ hay ic = iC − I CQ và 69Chương 4: Mạch phân cực transistor. vCE = vce + VCEQ hay v ce = vCE − VCEQ Vậy phương ngõ ra khi có nguồn tín hiệu ac là: 1 (iC − I CQ ) = − (vCE − VCEQ ) ( RC R L ) 1 VCEQ iC = − vCE + + I CQ (4.26) ( RC R L ) ( RC R L ) Phương trình 4.26 chính là phương trình đường tải ac của mạch hình 4.22. vậy đồ thị của phươngtrình đường tải ac chính là đường thẳng ACLL trên hình 4.27. Nhận xét: ACLL và DCLL luôn luôn gia o nhau tại điểm làm việc tĩnh Q. Hình 4.27: Đường tải ACLL , DCLL và dạng sóng tín hiệu vào ra. • Tầm dao động cực đại của tín hiệu ngõ ra (maxswing): Maxsing